플립플롭

- 전원이 공급되고 있는 한, 상태의 변화를 위한 신호가 발생할 때까지 현재의 상태를 그대로 유지하는 논리회로이다.

- 플립플롭은 레지스터를 구성하는 기본 소자이다.

- 기본적인 플립플롭은 2개의 NAND 또는 NOR 게이트를 이용하여 구성한다.

RS 플립플롭

- 플립플롭의 기본이다.

- S와 R선의 입력을 조절하여 임의의 Bit 값을 그대로 유지시키거나 무조건 0 또는 1의 값을 기억시키기 위해 사용한다.

JK 플립플롭

- RS 플립플롭에서 S=R=1일 때 동작되지 않는 결점을 보완한 플립플롭이다.

- 모든 플립플롭의 기능을 포함한다.

D 플립플롭

- RS 플립플롭의 R선에 인버터를 추가하여 S선과 하나로 묶어서 입력선을 하나만 구성한 플립플롭이다.

- 입력하는 값을 그대로 저장하는 기능을 한다.

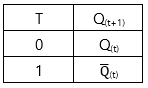

T 플립플롭

- JK 플립플롭의 두 입력선을 묶어서 한 개의 입력선으로 구성한 플립플롭이다.

- T=0 인 경우는 변화가 없고, T=1 인 경우에 현재의 상태를 토글시킨다.

- 원 상태와 보수 상태의 2가지 상태로만 서로 전환된다.

마스터-슬레이브(M/S) 플립플롭

- 출력측의 일부가 입력측에 FeedBack되어 유발되는 레이스 현상을 없애기 위해 고안된 플리플롭이다.

- 두개의 플립플롭으로 구성되는데 한쪽 회로가 마스터이고 다른 한쪽이 슬레이브 위치에 있다.

'<Certificate> > <정보처리산업기사>' 카테고리의 다른 글

| 주소 지정 방식(Memory Addressing Modes) (0) | 2020.08.20 |

|---|